临时文档

直链测试

一次切换重启

乱纪元

WINDOWS备忘录

5G模块

CLR20r3

蓝屏文件日志文件提取

CPU-Z

做个PE进入PE

英特尔桌面处理器对照表

PC各种档次电源转换效率区别

MM-Wiki

视频VIP解析

测试

野路子下载器

图片压缩

BIOS设置_核显 显示输出Auto、IGFX、PEG、PCI

电子应用要点

条件 定义 名称

图纸常用元器件速查

智能终端维修(在线学习600题

常见故障思路

BIOS

BGA

接口电路

充电电路/176

不触发不开机故障维修思路

EC刷写

6-10代时序

哎朋

MACBOOK信号

电路深度睡眠待机与主待机供电相关知识讲解

使用 Apple Configurator 2 修复或恢复基于 Intel 的 Mac - 官方 Apple 支持 (中国)

mac book通病

显卡工作过程

台式显卡

500时序 700时序

锐龙时序

台式机电源供电

电流检测 主供电

台式常见问题

15代处理器 800桥

常见通病常见笔记本

N卡功率检测芯片

本文档使用 MrDoc 发布

-

+

首页

500时序 700时序

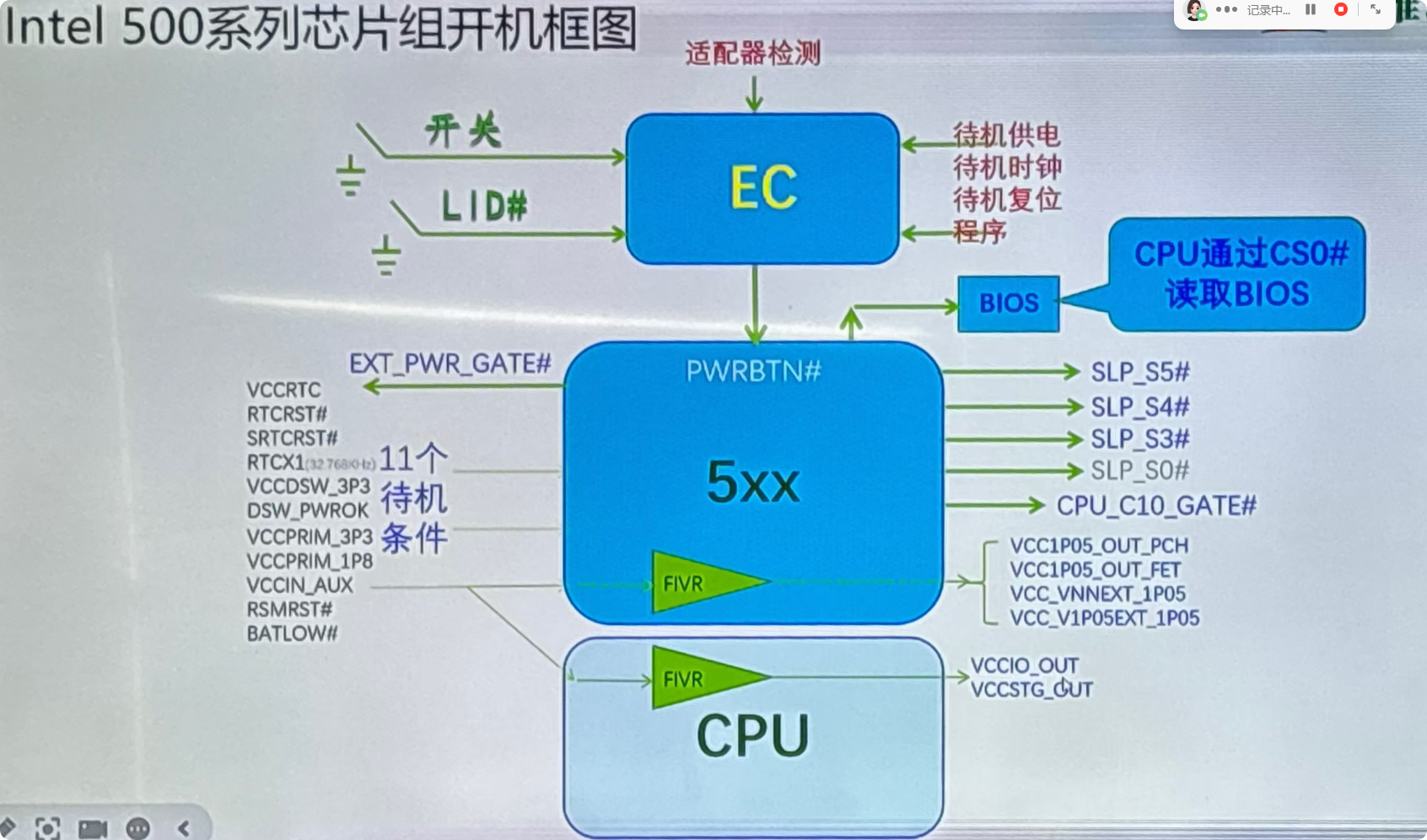

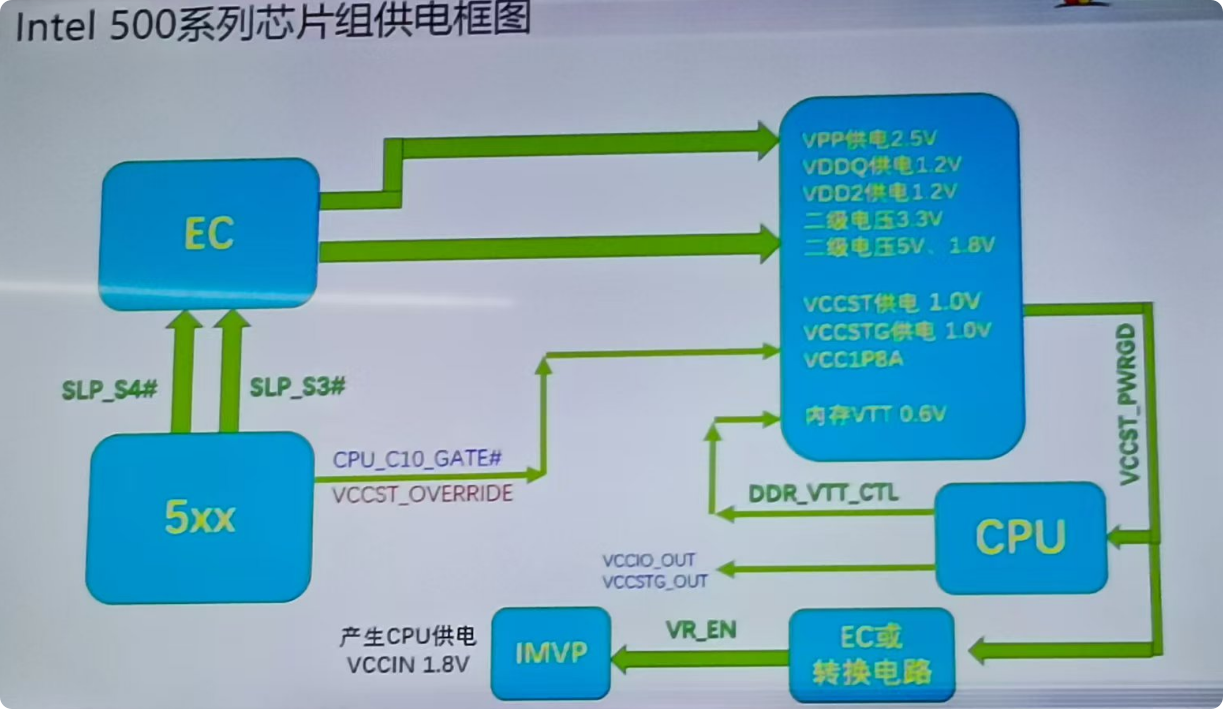

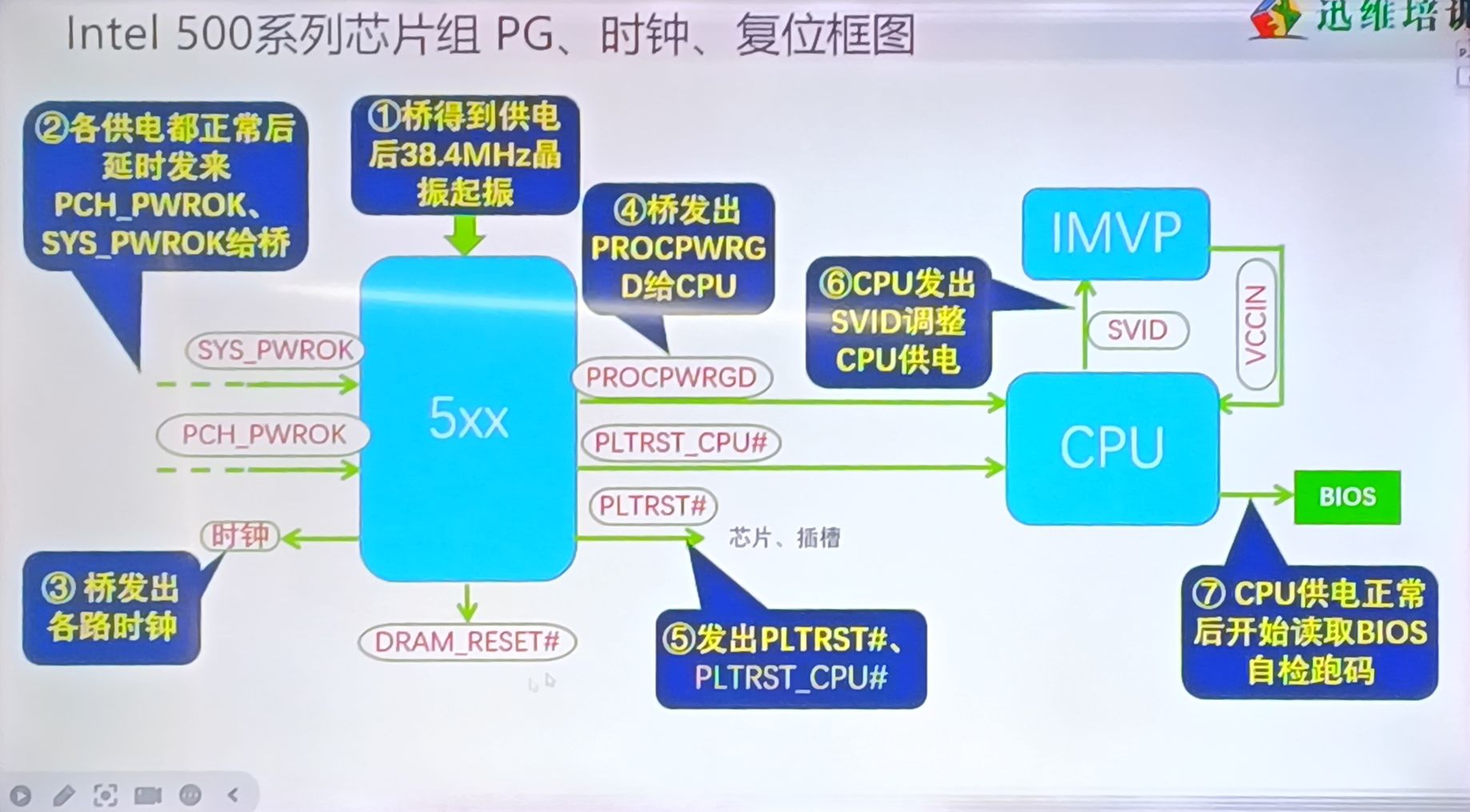

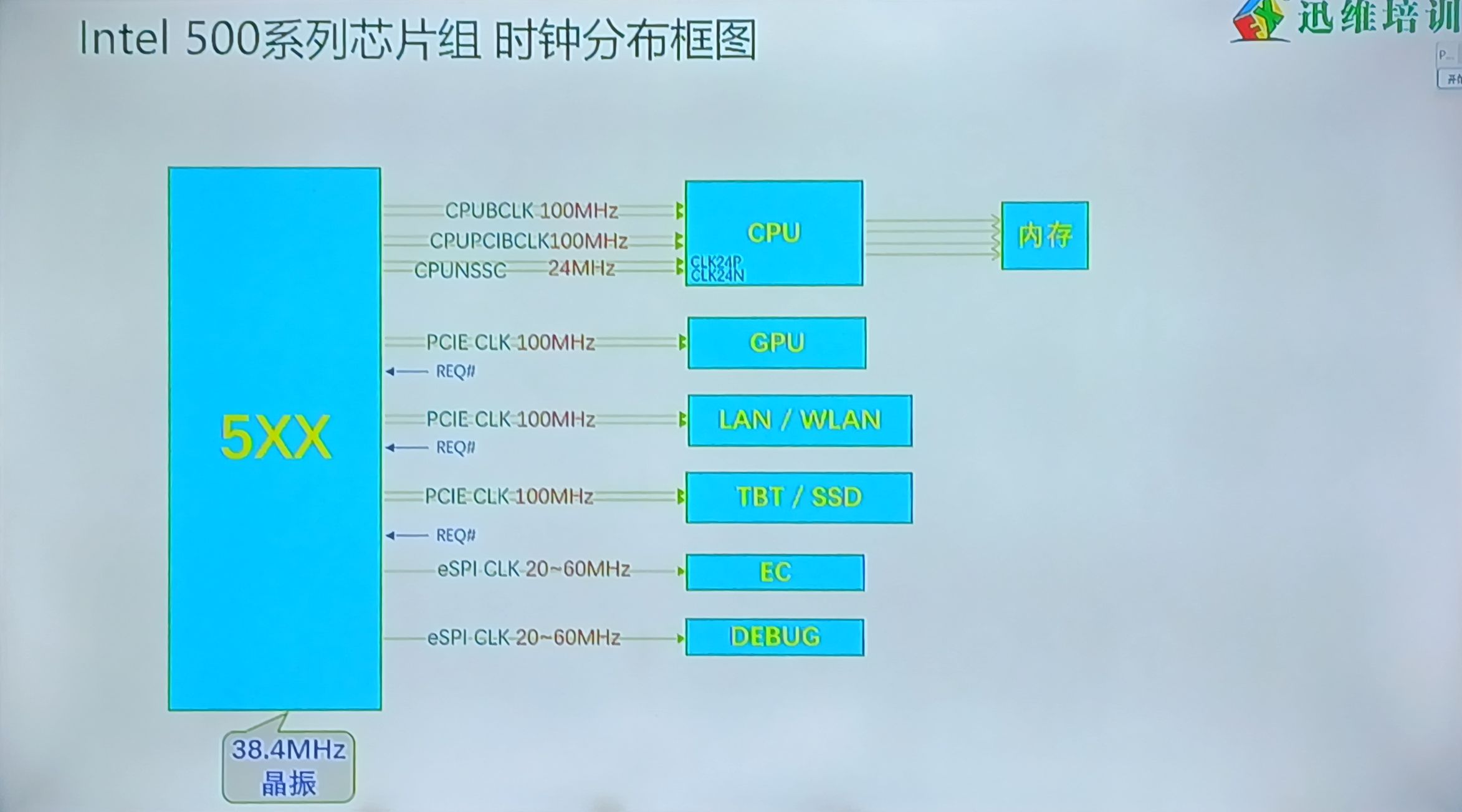

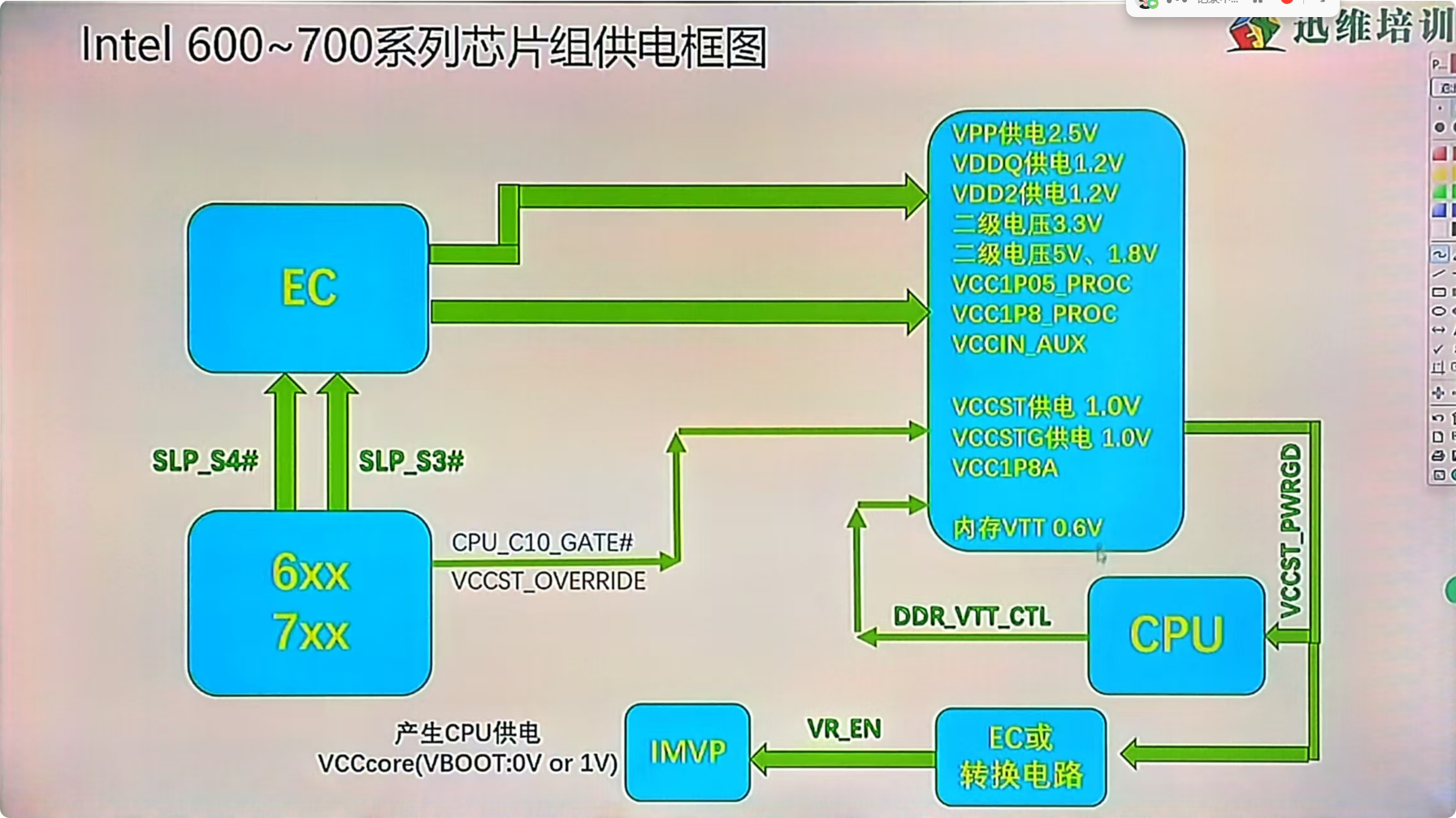

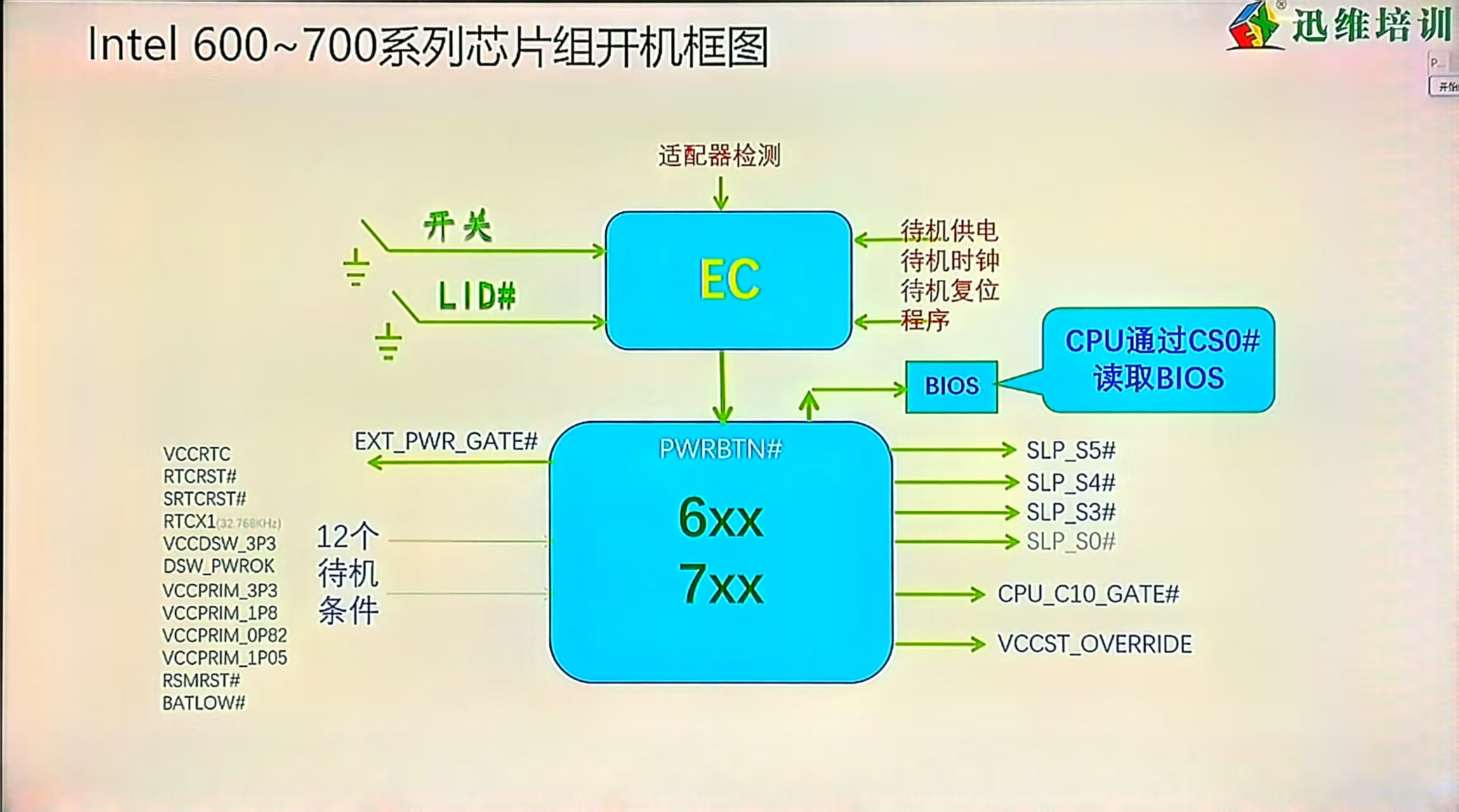

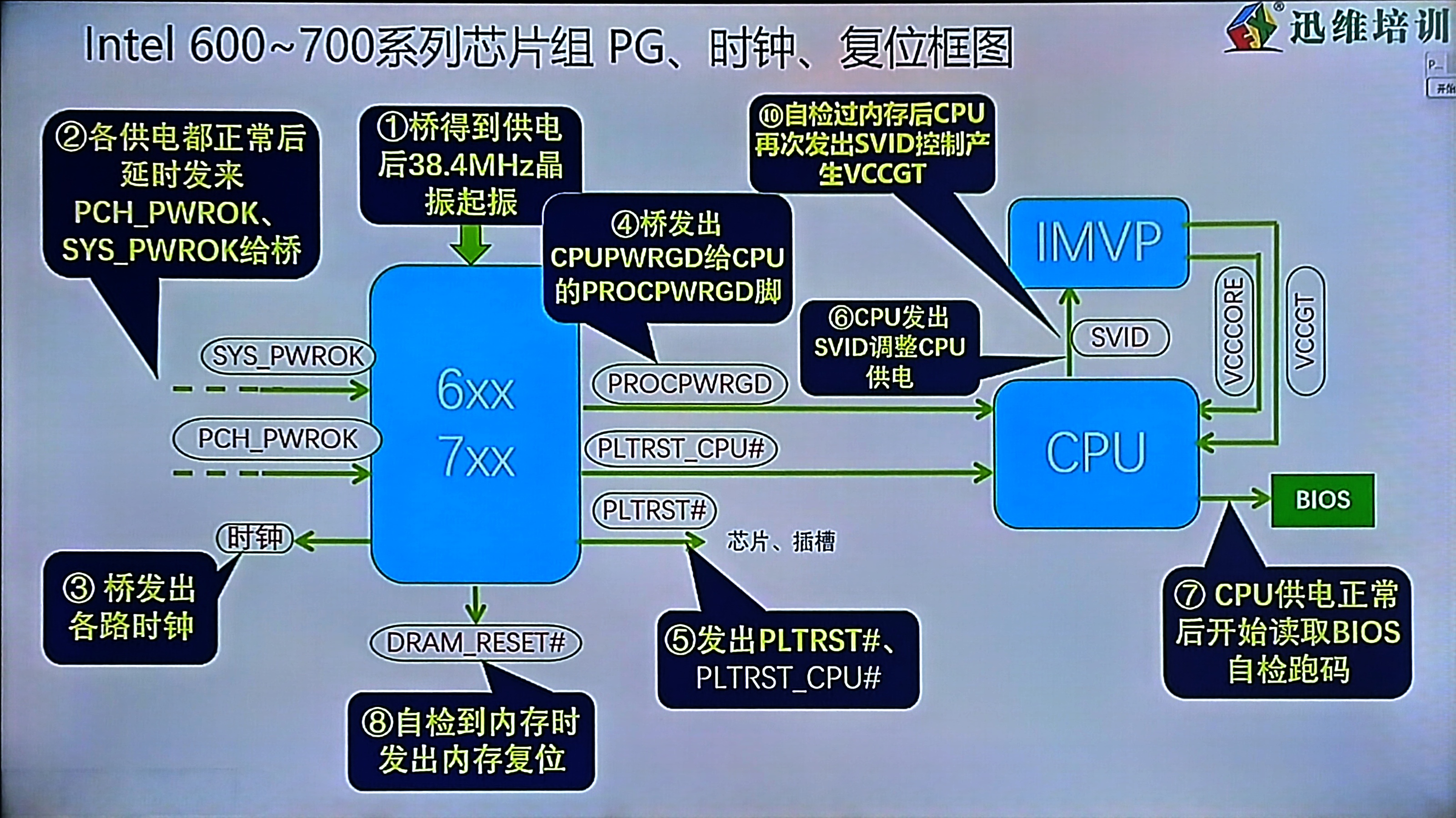

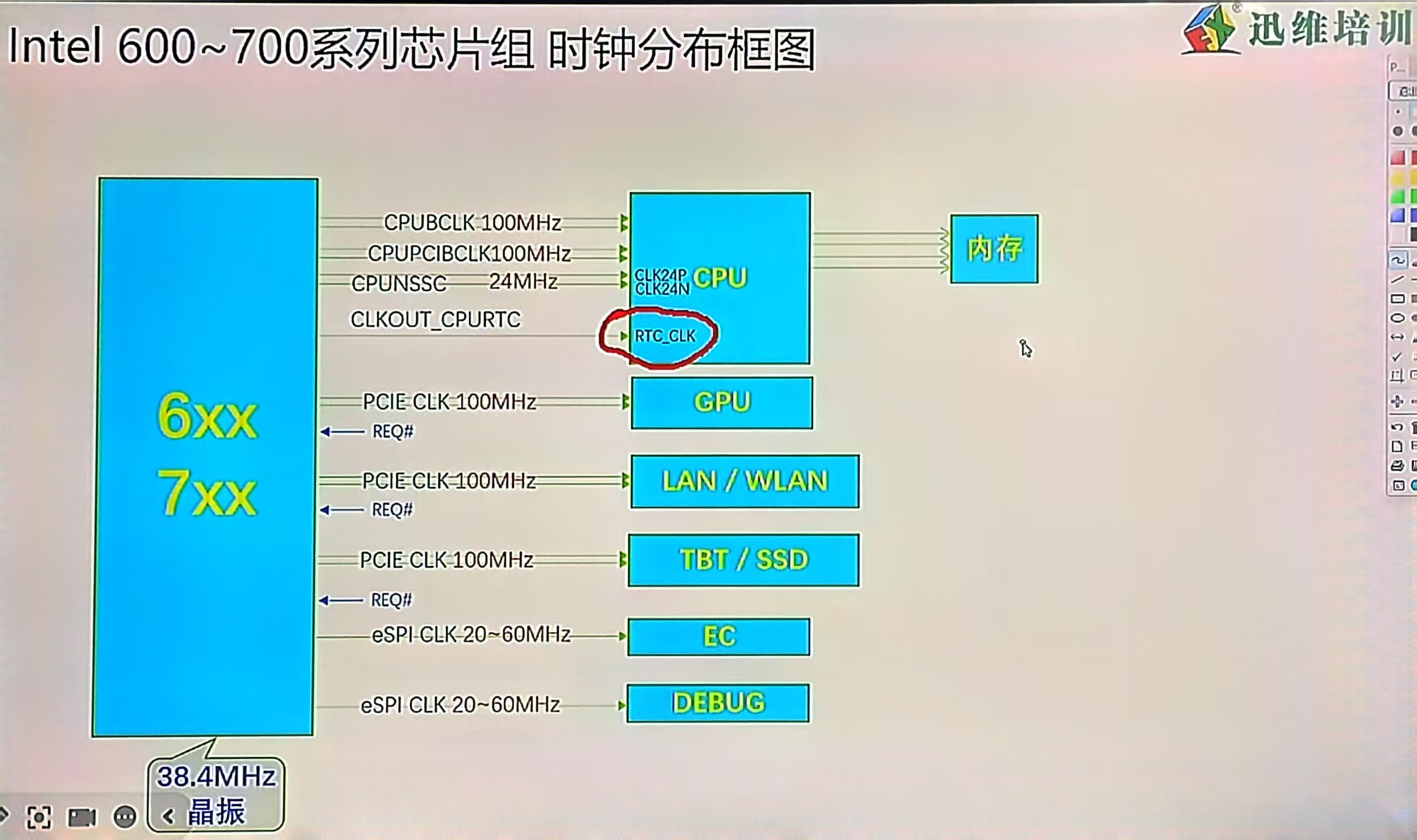

VCCRTC::从CMOS电池或主电池送给CPU的3V供电,给CPU芮RTC电路供电,以保存CMOS参数和时间运行。 RTCRST#/SRTCRST#:从主板送给CPU的两个RTC电路复位信号,3V以上高电平,复位时间通常不能低于18mS。 32.768Kz:CPU旁边的32.768Kz晶振,给CPU提供实时时钟频率。 VCCDSW3P3:CPU的深度睡眠待机电压,3.3V。不支持深度睡眠时,此电压与VCCPRIM3P3连一起。 DSW_PWROK:CPU的深度睡眠待机电压好,3.3Y。不支持深度睡眠时,此信号与RSMRST#连一起。 BATLOW#:电池电量低指示信号,通常来自EC,低电平时会导致不触发。包 SLP_SUS#:CPU发出的深度睡眠状态指示信号,可用于控制主待机电压(如VCCPRIM3P3)的开启和关闭。不支持深度睡眠时,SLP_SUS#悬空。 EXT_PWR_GATE#:外部电源控制信号,一般不采用。一般悬空 VCCPRIM3P3:CPU的主待机供电3.3V。`给桥的3.3,1.8主待机供电` VCCPRIM1P8:CPU的主待机供电1.8V。`给桥的1.8待机供电 待机时桥读不到BIOS无法产生` * VCCIN_AUX:给内部CPU和PCH的非核心FIVR供电(由`VCCIN_AUX、VCC_VNNEXT_1P05和VCC_V1P05EXT_1P05组成`)。fivr供电方式也叫全整合供电方式,桥内部的公共点 * VCC1PO5_0UT PCH/VCCIPO5 OUT_FET:CPU 内部输出的供电。 * RSMRST#:CPU的主待机电压好,3.3V,也是PCH内部ACPI控制器的复位,ACPI控制器VCCPRIM_.3P正常后开始复位,复位时间不能低于10S, * ESPI_RESET#:SPI总线复位信号 * VCC1P050_OUT_PCH/VCC1P05_OUT_FET:CPU内部输出的供电。`通过mos管转换给到vccsth和cpu` * SUSWARN#和SUSACK#:电脑进入深度睡眠状态的握手信号,如果电脑支持深度睡眠,当从S4/S5状态进入深度S4/S5状态时,由CPU内部PCH拉低SUSWARNA#这个信号送给EC或外部的逻辑电路,如果EC或外部逻辑电路认为可以关掉主特机电压,那EC或外部逻辑电路会拉低SUSACK#送给PCH作为应答,PGH将会拉低SLPSUS#,关掉主待机电压。 ESPI_RESETA#:SPI总线复位信号 SUSCLK:CPU发出的32.768z时钟,此信号不一定被主板采用。 ACPRESENT#:CP收到的适配器检测信号。 PRBN:CP收到的下降沿触发信号,通知桥退出睡眠状态。 SLPS5#:CPU收到PWRBT#后,置高SLPS5#成3.3V,表示退出关机状态。 SLPS4#:CPU置高SLPS4#成3.3V,表示退出休眠状态,用于开启内存供电。 SPS3#:CP置高SLPS3#成3.3Y,表示退出睡跟状态,进入S0开机状态,用于开启S0状态供电。 当PC和CPU处于空闲状态时,此信号将去控制CPU供电进入轻负载模式(低功耗模式)。也可以 SLP_SO#: SLP_LAN/SLP_WLAN#:有线网卡和无线网卡供电控制信号,用于控制VCC_LANPHY/VCC_WLANPHY供电的开启 连接到C,用于其它电源管理。 SLPA#:此信号一般不采用,因为CPU取消了ME模块供电 CPUC10_GATB#:当CPU进入C10状态(空闲状态)时,用于关闭VCCST、VCCSTG供电。 和关闭,一般不采用。 VCCST、VCCSTG:CPU的维持电压,通常受控于CPU_C10_CATE#。 PP、DD2、DDQ:指内存的VPP供电2.5V、VDD2和VDDQ供电1.2V,一般受控于SLPS4#。 V0C:指二级电压3.3Y、5V、1.8V等。 VCCST_PWRGD:送给CPU的电源好信号,指VCCST、VCCSTG、VDDQ供电正常,1.05V。 DDR_VTT_CTL:CPU发出的内存VTT供电开启信号,用于控制产生O.6V内存VTT供电。 RON:主板送给CPU电源管理芯片的开启信号,用于开启VCCIN供电给CPU。 VCCIN:CPU的FIVR供电 VCCIN_VR_READY::CPU的VCCIN供电正常,通常送给EC或其它PG相与。 PCH_PWROK:主板发给CPU的3.3Y高电平,表示S0状态电压都OK。 VCCI0N0UT:CPU输出的1.05供电 38.4Wz:各供电正常后,CPU的38.4W晶振起振,给CPU内部的时钟模块提供基准频率。 PCH_CLK_OUTPUTS:CPU输出各路时钟。 SYS_PWROK:表示系统供电正常,是产生复位的关键信号,电压为3.3V。 PLTRST#:CPU发出的平台复位3.3V,给各芯片、插槽作为复位。 CPU SVID:CPU发出SYID给CPU供电芯片,用于调整VCCIN供电,SVID信号由DATA和CLK组成的标准串行总 线和一个起提示作用的ALERT#信号所组成。 DRAM_RESET#:CPU满足了各个供电、时钟、复位信号后,开始读取BIOS自检(跑码),在自检过程中,当CPU 通过SMBUS完成内存识别后,CPU发出DRAM_RESET#给内存,用于复位内存。 ## 时序框图         ## 1. 700 系列芯片组的笔记本硬启动过程 ① 装入 3V 的纽扣电池后,产生 VCCRTC 给桥的 RTC 电路供电(4 大条件)。 ② 插上电池或适配器后,经过保护隔离电路,产生公共点。 ③ 接着产生 EC 的待机供电,在待机供电正常后,EC 给晶振供电产生 EC 待机时钟(也有的免晶振),待机供电延时产生 EC 待机复位(部分 EC 内部复位,如:KB9022/MEC1404),EC 读取程序配置自身脚位。 ④* 如果 EC 检测到适配器,会自动开启桥的深度睡眠待机电压(VCCDSW_3P3),并上拉BATLOW#; 然后 EC 延时发出DSW_PWROK给桥,通知桥深度睡眠待机电压好。 ⑤ 桥发出SLP_SUS#,把深度睡眠待机电压转换为主待机电压(VCCPRIM_3P3、VCCPRIM_1P8、VCCPRIM_0P82和VCCPRIM_1P05), 由主待机电压转换产生RSMRST#给桥,通知桥主待机电压已经正常。 ④* 如果 EC 检测到适配器,EC 会自动发出开启信号去开启桥待机供电:VCCDSW_3P3、VCCPRIM_3P3、 ⑤ EC 延时发出待机电压好,同时送给桥的 `DSW_PWROK` 和 `RSMRST#` 引脚,通知桥待机电压已经正常; 以上条件正常后,桥通过 SPT 总线读取 BIOS 配置脚位,并发出 ESPI 总线复位:`ESPI_RESET#`。同时通过 `CORE_VID0`/`CORE_VID1` 控制 `VCCIN_AUX` 供电。 ⑥ 按下开关,EC 收到开关信号后,延时发送一个 **高-低-高** 的开机信号给桥 `PWRBTN#` 脚。 ⑦ 桥发出高电平的 `SLP_S5#`、`SLP_S4#`、`SLP_S3#`、`CPU_C10_GATE#`、`SLP_A#`、`SLP_LAN#`、`SLP_DRAM#`…… 主板通过 **PMBUS** 往 CPU 供电芯片(CPU 核心供电、`VCCIN_AUX` 供电)内部写入程序(有些 CPU 供电芯片内部自带程序); ⑧ `SLP_S5#` 或 `SLP_S4#` 控制产生 **内存主供电**(供电在 DDR5 内存上)、`VDD2`;`SLP_S3#` 控制产生 **二级电压**(3.3V/5V 和 1.8V、`VCC1P05_PROC`、`VCC1P8_PROC`、`VCCIN_AUX` …… 等);`CPU_C10_GATE#` 控制产生 `VCCST` 和 `VCCSTG` 供电; ⑨ 供电正常后,产生 `VCCST_PWRGD` 信号送给 CPU,CPU 发出 `DDR_VTT_CTL` 信号控制产生 **内存 VTT 供电**(DDR5 内存不采用 `DDR_VTT_CTL` 信号控制 VTT 供电);CPU 发出 `VCCST_OVERRIDE` 用于保持 `VCC1P05_PROC` 供电一直开启。 ⑩ 各供电正常后,产生 CPU 供电的开启信号,控制输出 **CPU 核心供电**(`VBOOT` 有的 1V 左右,有的 0V); ⑪ 各供电正常后: - 桥的 **38.4M 晶振** 起振, - PG 汇总 **先后产生** `PCH_PWROK` 和 `SYS_PWROK` 送给桥; ⑫ 桥收到 `PCH_PWROK` 后,桥内部 **时钟模块** 完成初始化; ⑬ 桥发出 **各路时钟**; ⑭ 桥发出 `CPU_PWRGD` 给 CPU 的 `PROC_PWRGD` 脚; ⑮ 桥延时发出 **平台复位** `PLTRST#`(3.3V); 桥再发出 **CPU 复位** `PLTRST_CPU#` 送给 CPU 的 `RESET#` 脚; ⑯ CPU 发出 `SVID` 波形给 CPU 供电芯片调整(开启)**CPU 核心电压**; ⑰ CPU 供电正常,并得到复位后: - 通过 **DMI 总线** 发出寻址指令给桥, - 桥再通过 **SPI 总线** 读取 BIOS,原路返回给 CPU, - CPU 运行 BIOS 中的 **POST 自检程序**,开始对主板进行自检; ⑱ 自检到内存时: - 桥通过 **SMBUS** 读取内存 SPD 信息后, - 桥发出 **内存复位** `DRAM_RESET#`; ⑲ CPU 再次发出 `SVID` 波形给 CPU 供电芯片,控制产生 **集显供电** `VCCGT`(部分机器的集显供电会出现“瞬间开启后关闭”的情况)。

root

2025年7月30日 17:03

转发文档

收藏文档

上一篇

下一篇

手机扫码

复制链接

手机扫一扫转发分享

复制链接

Markdown文件

PDF文档(打印)

分享

链接

类型

密码

更新密码